揭秘,谁将成为瓜分未来CoWoS产能的赢家?

关于2026年CoWoS产能的分配问题,目前尚无法确定具体的瓜分情况,各方都在积极准备,以争取更多的市场份额,随着技术的不断进步和市场的不断变化,未来的CoWoS产能竞争将更加激烈,各家企业需要通过不断提升自身技术实力和市场竞争力来争取更多的份额,具体结果还需待市场进一步发展和变化后才能揭晓。

当晶体管微缩逼近物理极限,先进封装便成为决定芯片性能的“第二核心阵地”。

而EMIB的出现,恰逢其时。

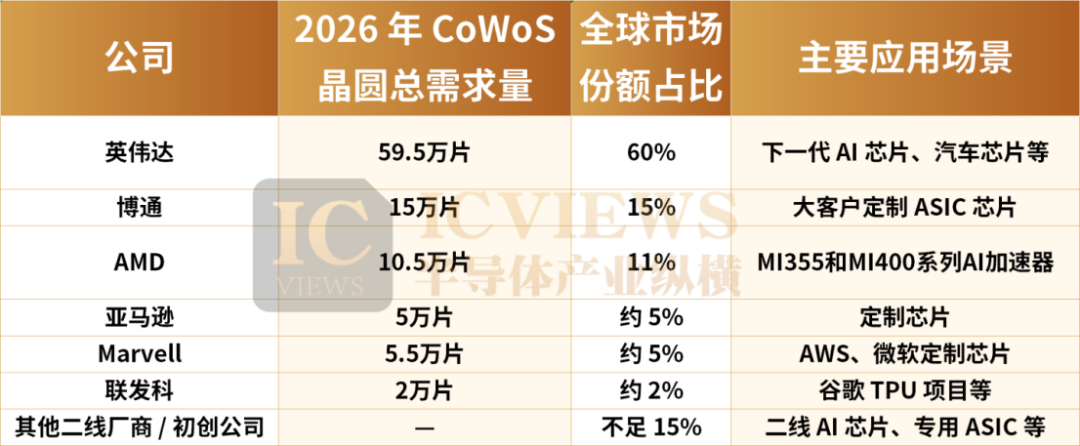

01 2026年CoWoS产能,被谁瓜分?

CoWoS(Chip-on-Wafer-on-Substrate),是AI时代名副其实的“香饽饽”。

作为台积电在“超越摩尔定律”道路上的核心技术,Chip-on-Wafer(CoW)工艺将多个芯片(如GPU、CPU和HBM等)堆叠并键合到硅中介晶圆上;然后,再将CoW芯片与封装基板(Substrate)整合,形成完整的CoWoS封装结构。

这意味着它允许将采用5nm/3nm先进制程的GPU计算单元、专为存储优化的HBM芯片,以及成熟制程的I/O接口芯片整合为单一系统级封装,在性能、功耗与成本间找到最佳平衡点。

在AI算力竞赛中,CoWoS的高带宽优势更是不可或缺。数据显示,采用CoWoS封装的AI芯片与HBM间的数据传输带宽可达TB/s级别,较传统封装提升一个数量级,完美解决了“内存墙”问题,成为高端AI训练芯片的标配。

随着ChatGPT等大模型迭代加速,全球云端AI芯片需求呈爆发式增长,全球CoWoS总需求将从2024年的37万片,增长至2025年的67万片,并在2026年达到100万片,这种爆发式增长进一步加剧了产能缺口。

目前来看,仅少数AI芯片龙头企业具备大规模“锁定产能”的实力,其余专用芯片(ASIC)厂商及二线AI芯片企业,均面临CoWoS产能获取不足的困境。

日前摩根士丹利报告预测,到2026年,英伟达的CoWoS晶圆总需求量将达到59.5万片,占全球总需求的60%。这笔庞大的订单中,约51万片将由台积电承接,主要用于下一代Rubin架构芯片。据此推算,2026年英伟达芯片出货量可达540万颗,其中240万颗将来自Rubin平台。Amkor和日月光(ASE/SPIL)等外包封测厂(OSAT)也将为英伟达分担约8万片的CoWoS产能,主要用于其Vera CPU及汽车芯片等产品。

紧随其后的是博通,预计需求达15万片,占总需求的15%。其产能主要服务于大客户的定制芯片(ASIC),包括为谷歌TPU预订的9万片(台积电8.5万片,日月光/矽品5千片)、为Meta预订的5万片,以及为OpenAI预订的1万片。

AMD预计将获得10.5万片CoWoS晶圆,占据约11%的市场份额。其中,8万片将在台积电生产,用于其MI355和MI400系列AI加速器。

其他玩家包括亚马逊、Marvell、联发科等。其中亚马逊通过其合作伙伴Alchip预订了5万片;Marvell为AWS和微软的定制芯片预订了5.5万片;联发科(MediaTek)为谷歌TPU项目预订了2万片。

综合来看,上述几大客户已锁定台积电CoWoS总产能的85%以上,留给二线AI芯片厂商、专用ASIC企业及初创公司的份额不足15%。在排期普遍延后至2026年甚至更晚的背景下,产能稀缺已从技术瓶颈演变为市场准入门槛。

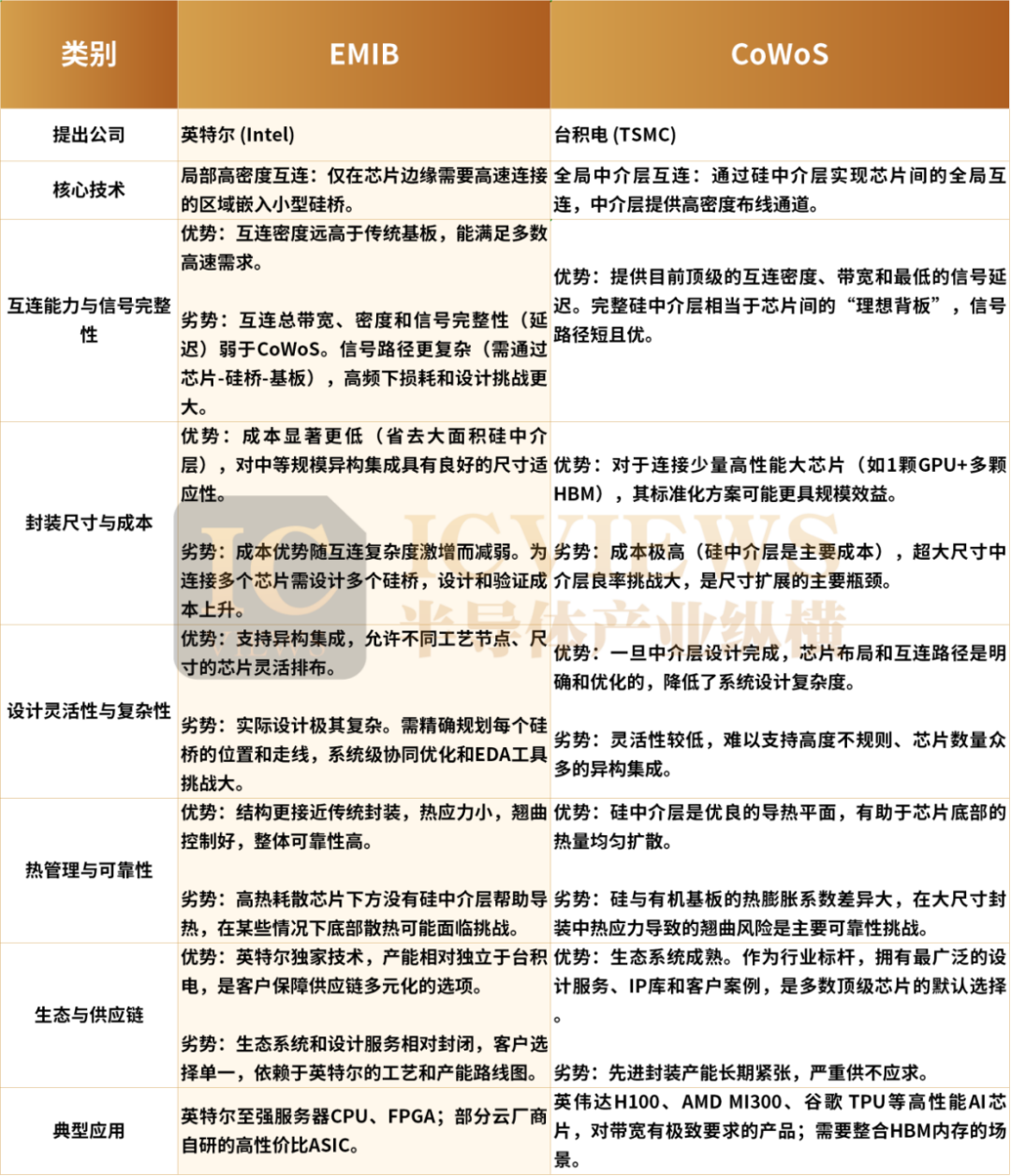

当CoWoS成为少数巨头的专属资源,一个现实问题需要被重新考虑:除了CoWoS,还有没有其他选择?

02 英特尔EMIB,突袭!

英特尔(Intel)的EMIB先进封装正成为芯片企业的备选方案之一。

相较于CoWoS,EMIB拥有数项优势。

首先是结构简化,EMIB舍弃昂贵且大面积的中介层,直接将芯片使用内嵌在载板的硅桥(Bridge)方式进行互连,简化整体结构,相对于CoWoS良率更高。

其次是热膨胀系数(Coefficient of Thermal Expansion, CTE)问题较小,由于EMIB只在芯片边缘嵌硅桥,整体硅比例低,因此硅与基板的接触区域少,导致热膨胀系数不匹配的问题较小,较不容易产生封装翘曲与可靠度挑战。

最后EMIB在封装尺寸也较具优势,相较于CoWoS-S仅能达到3.3倍光罩尺寸、CoWoS-L目前发展至3.5倍,预计在2027年达9倍;EMIB-M已可提供6倍光罩尺寸,并预计2026到2027年可支援到8倍至12倍。价格部分,因EMIB舍弃价格高昂的中介层,能为AI客户提供更具成本优势的解决方案。

然而,EMIB技术也受限于硅桥面积与布线密度,可提供的互连带宽相对较低、讯号传输距离较长,并有延迟性略高的问题。

英特尔自2021年宣布设立独立的晶圆代工服务(Intel Foundry Services, IFS)事业群,耕耘EMIB先进封装技术多年,已应用至自家Server CPU平台Sapphire Rapids和Granite Rapids等。

EMIB关注度提升的背后,是以谷歌为代表的ASIC方案之崛起。

据悉,Marvell美满和联发科已考虑将英特尔的EMIB先进封装纳入ASIC芯片设计的可选项中,谷歌也决定于2027年的TPU v9 AI芯片中导入英特尔EMIB先进封装试用。苹果、博通和高通也可能很快成为英特尔晶圆代工业务的客户。三家公司招聘信息显示,招聘封装工程师的关键要求之一是掌握英特尔EMIB技术,这表明这些公司急于招聘熟悉英特尔EMIB技术的工程师,助力下一代产品设计。

其中苹果以自研云端ASIC为核心方案,高通则聚焦Tier 2 AI加速卡产品,二者的应用场景均无需依赖CoWoS封装;相比之下,EMIB封装具备更优成本效益,反而能更好适配其产品需求。此外,对于运算需求相对较低的ASIC推论场景,EMIB封装同样具备技术支持能力。

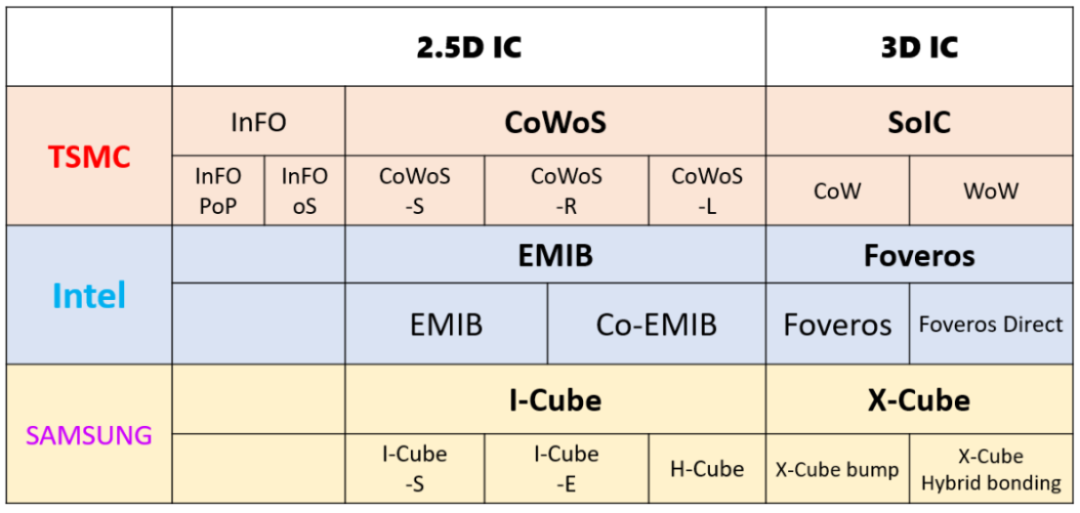

03 先进封装,三强混战

EMIB的崛起,正将先进封装市场拖入“台积电、英特尔、三星”的三强混战。

台积电方面,有一点需要特别注意,台积电2026年CoWoS产能的大客户大都属于美国公司,如今美国客户希望实现全产业链的在美生产,但台积电和上下游暂无可用的在美后端产能。

今年中旬,市场消息称台积电正在大规模推进在美生产计划,包括建设晶圆厂、研发中心和先进封装设施。除芯片制造外,CoWoS等先进封装技术是供应链中最关键的环节之一。据报道,台积电似乎正将战略重心转向该领域,计划2026年启动封装厂建设,预计将于2029年竣工投产。

该封装厂将选址在亚利桑那州,台积电已开始招募CoWoS设备服务工程师。这座先进封装工厂将负责生产CoWoS及其衍生技术,以及SoIC和CoW等下一代封装方案,这些技术将应用于英伟达Rubin系列和AMD Instinct MI400等产品线。根据初步规划,亚利桑那州的封装厂将与当地晶圆厂实现联动,因为SoIC等产品需要使用带有中介层(interposer layer)的芯片。

三星也在趁机搅局。三星的先进封装技术体系分为2.5D的I-Cube和3D的X-Cube两大系列。其中X-Cube作为三星3D封装的核心,通过TSV技术实现芯片垂直电气互连,分为凸点互连和混合键合两种工艺路径。

此外,三星电子先进封装(AVP)部门还正在主导开发“半导体3.3D先进封装技术”,目标应用于AI半导体芯片,2026年第二季度量产。该技术通过安装RDL中介层替代硅中介层来连接逻辑芯片和HBM;并通过3D堆叠技术将逻辑芯片堆叠在LLC上。三星预计,新技术商业化之后,与现有硅中介层相比,性能不会下降,成本可节省22%。三星还将在3.3D封装引进“面板级封装(PLP)”技术。

真正的变量在英特尔。今年英特尔代工大会上,英特尔公布了EMIB技术的新变体—— EMIB-T,其中T指的应是TSV硅通孔;此外还有分别采用RDL重布线层和Bridge桥片的Foveros-R、Foveros-B封装。这一面向HBM4、UCIe芯片集成的工艺通过TSV和M Bridge技术在基板中构建垂直的电力通道,而不会像传统方案一样需要“绕路”。这意味着EMIB-T可实现更低的直流/交流电噪声,有利于信号传输的稳定性。

英特尔表示EMIB-T支持从其它2.5D先进封装技术迁移,同时这一过程无需重大重新设计。对于未来的EMIB,英特尔预告其到2026年可通过超过20个EMIB桥实现约120mm×120mm的总封装尺寸,集成12个HBM内存堆栈;而到2028年,封装尺寸将进一步扩展到120mm×180mm,HBM数量将超过24个。

全球第二大OSAT(外包封测)企业Amkor安靠在今年的英特尔代工Direct Connect大会上曾宣布与英特尔建立战略合作伙伴关系,Amkor将在其多地制造工厂采用EMIB封装工艺,为EMIB建立替代来源。据悉,Amkor决定在其韩国仁川松岛K5工厂建设EMIB产能,这是因为此地的设备足以满足EMIB先进封装工艺的需求,同时现有的材料、零部件、人才资源丰富。

消息人士表示,Amkor韩国仁川松岛K5工厂不仅将承担英特尔产品部门芯片的EMIB封装,也将为英特尔代工的外部客户提供服务。除韩国外,Amkor的葡萄牙和美国亚利桑那州制造工厂也将导入英特尔EMIB工艺。

据Yole数据,预计2025年全球先进封装市场规模占比将首次超过传统封装,达到51%,并持续以10.6%的CAGR增长至2028年的786亿美元。EMIB的崛起正在打破“一家独大”的格局。

与此同时,EMIB的崛起并不意味着CoWoS的衰落,而是先进封装行业迈入场景化精准匹配的新发展阶段。CoWoS在互联密度和超高频段信号完整性上的优势,仍是英伟达、AMD等高端GPU厂商的核心需求,短期内难以被替代。而EMIB则在ASIC、中端AI芯片等领域或可打开增量空间。